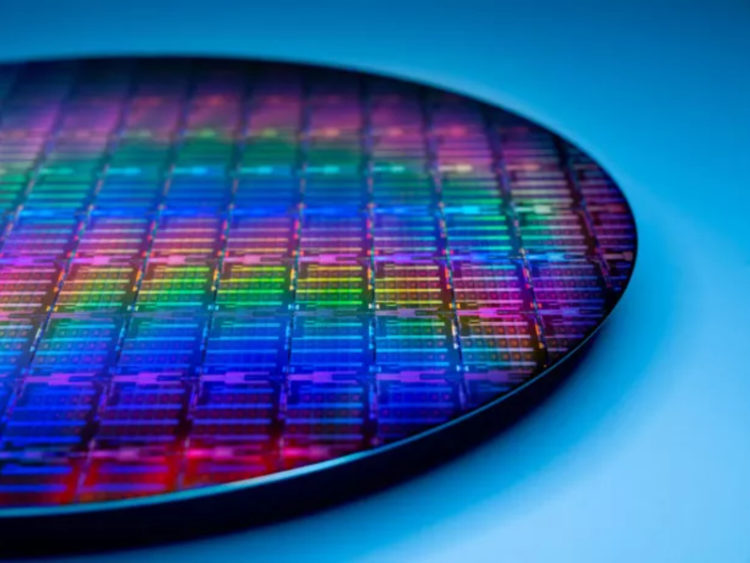

Apple dan Intel dikabarkan akan menggandeng TSMC untuk memproduksi prosesor berbasis 3nm mereka. Langkah ini berbeda dengan Qualcomm, yang dikabarkan akan menggandeng Samsung untuk membuat SoC berbasis 3nm mereka.

Seperti diketahui, TSMC saat ini sedang menguji coba teknologi fabrikasi 3nm mereka. Seperti beberapa kabar sebelumnya, mereka akan menggunakan teknologi bernama N3 untuk memproduksi chipset tersebut.

TSMC pun dikabarkan baru akan memulai produksi chipset berbasis 3nm tersebut di pertengahan 2022 mendatang. Jadi, kemungkinan besar prosesor yang diluncurkan tahun ini akan masih menggunakan teknologi fabrikasi 5nm.

Apple dikabarkan akan menggunakan teknologi fabrikasi 3nm ini untuk membuat jajaran prosesor untuk perangkat iPad mereka. Ada kemungkinan, Apple akan menggunakan teknologi fabrikasi N3 generasi pertama ini untuk prosesor Macintosh mereka.

Soalnya, SoC yang ada di perangkat iPad mereka memiliki performa yang sama dengan chipset M1 yang ada di perangkat Macintosh dengan spesifikasi dasar atau menengah yang ada saat ini.

Di sisi lain, Intel dikabarkan akan menggunakan teknologi fabrikasi 3nm untuk CPU untuk PC dan server. Mereka dikatakan sedang mempersiapkan setidaknya dua produk yang dibuat menggunakan node N3 TSMC, satu ditujukan untuk notebook, satu lagi untuk server.

Tidak ada rincian tentang prosesor ini saat ini, tetapi Intel telah secara tidak sengaja mengkonfirmasi prosesor Xeon terbaru akan dibangun dengan bantuan TSMC. Beberapa bulan yang lalu mereka mengatakan akan bekerja dengan TSMC untuk membuat prosesor yang akan diluncurkan pada 2023 mendatang.

Selain itu, Apple dan Intel saat ini sedang dalam tahap ‘menguji desain chip’ yang didasarkan proses N3 TSMC. Dikarenakan TSMC sudah mulai melakukan uji coba, kemungkinan besar Intel dan Apple sudah menyelesaikan desain mereka.

Proses manufaktur N3 TSMC adalah teknologi baru yang akan memberikan peningkatan PPA (kinerja, daya, area) jika dibandingkan dengan N5. Teknologi ini menjanjikan peningkatan kinerja 10% hingga 15% pada daya dan jumlah transistor yang sama.

Selain itu, teknologi ini juga akan mengurangi penggunaan daya hingga 30% pada kecepatan clock dan kompleksitas yang sama, memberikan peningkatan kepadatan logika hingga 70%, dan hingga 20% Keuntungan kepadatan SRAM. N3 akan agresif menggunakan litografi ultraviolet ekstrim (EUVL) untuk ‘lebih dari 20 lapisan’.